# 負帰還前置増幅回路とクロックドインバータ識別再生回路の一体化設計による 1Gbit/s 高速受信回路の低消費電力化の検討

Examination for Low Power Consumption Receivers operating at 1Gbit/s by Integrated Design of Negative-feedback Preamplifiers and Clocked Inverter Decision and Regeneration Circuits

> 大川 典男 <sup>1)</sup> 一澤 春希 <sup>2)</sup> Norio Ohkawa<sup>1)</sup> Haruki Ichizawa <sup>2)</sup>

#### Abstract:

Low-power consumption digital receivers are required due to development of optical communication systems and wireless sensor network systems. Digital receivers generally have 3R functions (Reshaping; equalizing and amplification, Retiming; timing extraction, Regeneration; decision and regeneration). A performance index API that evaluates bandwidth, gain, and power consumption collectively and expresses efficiency, has been applied to various amplifiers that operate in analog. In order to find the maximum API values of those amplifiers in a short time, a method that can change the circuit parameters to multi-step while keeping the operating point fixed, is applied. This time, gate width of the amplification FETs is added to the circuit parameters, and the maximum API values of the voltage-current type, current-voltage type negative feedback amplifiers are obtained through the API support program, which was previously developed.

The maximum API of the voltage-current type feedback amplifier is about 1.4 times larger than that of the current voltage type, found to be that the main factor is due to bandwidth characteristics.

Next, the clocked inverter CMOS D-FF, which has excellent high-speed operation, is applied to the decision and regeneration circuits of the digital receivers. Among the various feedback amplifiers examined, the ones with the largest API at each gate width and a bandwidth of about 1 GHz or more are used as pre-amplifiers with reshaping function. By integrating the decision and regeneration circuit and the pre-amplifier circuit, the circuit configuration and circuit parameters that enable high-speed operation of 1 Gbit/s and have the lowest power consumption of the entire circuit are obtained.

From the above, it is clarified the API performance of various circuit parameters including gate width of the amplification FETs for the voltage-current type feedback amplifier. Finally, a clocked inverter CMOS D-FF with excellent high-speed operation and a voltage-current type amplifier is integrated, and is clarified the circuit configuration and the circuit parameters that have the lowest power consumption in the high-speed operation range of 1 Gbit / s.

Keywords: Negative-feedback amplifier, Low-power consumption, Clocked Inverter, Decision voltage, Voltage-current feedback

# 1. まえがき

光波長多重技術による光ファイバ1本当たり1000波長の光伝送実験[1],空間分割多重技術による光ファイバ1本当たり7コアのマルチコアファイバを用いた中継増幅光伝送実験[2]など,今後さらなる大容量化の研究開発の進展が期待されている.このような光通信システムに適用される受信機は,波長数×コア数に相当する数が必要となり,高速化のみならず低消費電力化も重要な課題となっている.さらに, IoT (Internet of Things) 用のネットワークデバイスは今後急速に数を増やし,最終的には毎年1兆個を超えるセンサーネットワークデバイスを活用する時代が到来すると予想されている[3].ワイヤレスセンサーネットワークを利用した様々なサービスの多くは屋外

にセンサーが設置されることも多く,管理コストの観点からバッテリーレスで動作可能なワイヤレスセンサー用送受信器が強く要望されている.このため,搬送波や環境電波からの給電で駆動できる極低消費電力化された送受信器の実現が求められている.

これらの光通信システムやワイヤレスセンサーネットワークではディジタル信号が用いられ、それらに共通したディジタル受信機は一般的に 3R 機能 (等化増幅,タイミング抽出,識別再生)を有している.アナログ動作をする等化増幅回路では帯域,利得,消費電力を一元的に評価する性能指標 API を提案し[4],様々な増幅回路の性能評価を行ってきた.API を計算するためには,回路パラメータを変更する毎に帯域,利得,消費電力を求める必要がある.最も基本的な1段のソース接地増幅回路においても,ドレイン側に印加する電源電圧,ゲート-ソース間電圧,負荷抵抗の3つの回路パラメータが存在し,回路の効率が最も高くなる API 最大値は,これらの回路パラメータをどのように変更して求める必要があり,回路パラメータをどのように変更したら API 最大値に近づけるか,見通しがなければ膨大な数の API 計算が必要となる. 効率よく API 最大値を

<sup>1)</sup>東京都立産業技術高等専門学校ものづくり工学科電子情報工学コース

<sup>&</sup>lt;sup>2)</sup>東京都立産業技術高等専門学校専攻科創造工学専攻電気 電子工学コース

求めるため、動作点固定解析法を考案し、nMOSFET を適用した各種負帰還増幅回路(電圧-電流型、電流-電圧型、電 圧-電圧型、電流-電流型)の電源電圧、ゲート電圧、負荷抵抗、帰還抵抗、帰還インダクタ、ピーキング抵抗、ピーキングコンデンサを回路パラメータとして、各種負帰還増幅回路の API 最大値を求めた[5]. 今回、個別部品としてのnMOSFET を前提としていた  $270[\mu\,m]$  に固定されていたゲート幅を、今後のモノリシック IC 化を念頭として新たな回路パラメータに加えた. ゲート幅固定時に最も API の大きかった電圧-電流型帰還増幅回路と、次に API の大きかった電流-電圧型帰還増幅回路について、ゲート幅を回路パラメータに加えた場合の API 最大値を求める.

なお、高速動作に優れた識別再生回路であるクロックドインバータ CMOS D-FF のディジタル受信器の識別再生回路への適用は検討済である[6]. 検討した負帰還増幅回路の内、最も API が大きくかつ 1[GHz]程度以上の帯域幅が得られたものを等化増幅機能を持つ前置増幅回路として、クロックドインバータ識別再生回路と前置増幅回路を一体化設計することで 1Gbit/s の高速動作が可能でかつ、回路全体として最も低消費電力となる回路構成と回路パラメータを明らかにする.

# 2. 評価方法

最初に nMoSFET のゲート幅を回路パラメータに加えた電圧-電流型帰還増幅回路,電流-電圧型帰還増幅回路の性能比較は, SIMetrix による回路シミュレーションにて実施する.この回路シミュレータは, SPICE3 をベースとし,収束性に優れ,短ゲート長 MOSFET であるゲート長0.18[ $\mu$ m],かつゲート幅が可変可能な nMoSFET デバイスモデル (T85S) に対応している.特性パラメータである3dB 帯域幅,電圧利得,消費電力を回路シミュレーションにより求め,それらの特性パラメータを一元的に評価でき,効率を表す増幅回路の性能指標 API の最大値をそれぞれの負帰還増幅回路について求め,相互比較を行う.

次に識別再生回路に高速動作領域で低消費電力に優れ たクロックドインバータ CMOS D-FF[7]に最も大きな API の得られた負帰還増幅回路を前置増幅回路として付加し, 一体化回路として評価を行った. 一体化回路のフロントエ ンドとなる前置増幅回路への入力信号は,シミュレータの 収束速度を考慮して7段のPRBS テストパターンとしたが、 基幹伝送路では7段のスクランブラをかけており、この段 数でも最低限必要とされるランダム性は確保されている. 動作速度は高速動作領域といえる 1Gbit/s に設定した.信 号電力の強さは、比較的強い信号を想定した-20[dBm]と、 比較的弱い信号を想定した-40[dBm]の 2 種類を想定 し、 $50[\Omega]$ 負荷による電圧変換を行い、それぞれの入力信 号電圧を 45[mVp-p], 4.5[mVp-p]とした. 前置増幅回路 に必要な電圧利得は,前置増幅回路への入力電圧と識別再 生回路の入力電圧である識別電圧からから決定される. 識 別電圧を大きくするほど、識別再生回路の消費電力は低 減される傾向にあるが[6],この場合前置増幅回路の電圧 利得を大きくする必要があり,前置増幅回路の消費電力が 増大してしまう.一体化回路全体として低消費電力化を図 るためには,一体化時に最適な識別電圧を検討する必要が ある. 前置増幅回路に適用する各種負帰還増幅回路の縦続 接続段数と最適な回路パラメータは、所要帯域幅と電圧利 得を確保した上での低消費電力化を図る観点から求値し

た. 前置増幅回路と識別再生回路の一体化回路を評価するには、まず一体化回路の出力が所要の符号誤り率(BER)特性を満たす必要がある. ここでは、基幹伝送システムにおいて設計されている BER 規定値を参考に、前方誤り訂正(FEC)を行う前の所要 BER を 10<sup>-4</sup> 以下とした. 所要 BER を満たした上で、一体化回路全体として最小となる消費電力が得られる前置増幅回路の構成や回路パラメータを求めた.

## 2.1 性能指標 API の概要とマルチステップ解析

増幅回路の性能を効率という観点から評価するため,次式で定義される性能指標 API[4]を各種負帰還増幅回路の性能比較に適用する.

$$API = \frac{G \cdot B}{W} \qquad [(dB \cdot Hz)/W] \tag{1}$$

ここで, Gは dB表示した電圧利得[dB], Bは 3dB帯域幅 [Hz], Wは消費電力 [W]である. Gを dB 表示とすることに より,利得と損失の境界は 0 となる. B, W は負とならない ため、Gの正負、すなわち API の正負の判定により、増幅器 と減衰器を明確に区別することが可能となる. API は単 位消費電力当たりの利得帯域幅積, すなわち, 増幅回路の 効率を表した指標であると言える. これより API が正で大 きい程、効率の高い増幅回路であると言う事ができる. 増幅回路は回路パラメータにより特性パラメータが変化 するので、SIMetrix のマルチステップ解析で回路パラメ ータを変化させて API が最も大きくなる値と, そのときの 回路パラメータの求値を行う.着目した一つの回路パラメ ータのみを変化させ,他の回路パラメータを固定する従来 のマルチステップ解析では,回路パラメータの変化ととも に、MOSFET にかかるドレイン-ソース間電圧 Vos とゲート-ソース間電圧 VG から決まる動作点も変動する.このため 1回のマルチステップ解析を行い、その中で最も大きな API (API 極大値) が得られる回路パラメータが求まった としても,他の回路パラメータを別の値に固定して,同様 に着目した一つの回路パラメータによるマルチステップ 解析を繰り返した場合、それぞれ動作点が変わってしまい API 最大値が得られる回路パラメータ値を予測し難く,メ ッシュ状に多くの解析点を取らなければ API が最大とな る回路パラメータ値を求め難いという難点があった.この 問題点を解決するため動作点固定解析法[5]を導入した. これは着目した回路パラメータと動作点を変動させる他 の回路パラメータを関連付けて同時に変化させることに より、マルチステップ解析を行っても動作点が固定され る解析方法である.

動作点固定解析法を用いることにより、1回のマルチステップ解析でその動作点で最も大きな API 値(API 極大値)を求めることができる.動作点を変えて同様に動作点固定解析法によりその動作点での API 極大値を求め、着目した動作点での API 極大値がその周り 8点( $V_{OS}$ が同じで  $V_{OS}$ が大きい、または小さい場合、 $V_{OS}$ が大きく  $V_{OS}$ が大きい、または同じ、または小さい場合、 $V_{OS}$ が小さく  $V_{OS}$ が大きい、または同じ、または小さい場合)の中で最も大きい、カーンジスタの動作点に対する API 値のピークは 1つだけであるため[4]、着目した動作点での API 極大値が、動作点間隔の精度において API 最大値であると言うことができる.動作点間隔を狭めることにより、API 最大値とその動作点の精度を向上させることが可能である.

# 2.2 一体化回路の BER と消費電力の評価

回路シミュレーションによる前置増幅回路と識別再生 回路の一体化回路の BER 評価系は,参考文献[8]に示すと おりである. PRBS 発生部は, D-FF を縦続接続して構成し たシフトレジスタと EX-OR を組み合わせることで最大長 周期系列を発生する符号器として実現できるが,回路シミ ュレータのライブラリでは D-FF はディジタル信号として 出力されるので, D/A コンバータを介し, 電圧振幅を可変 とすることが可能なアナログ信号に変換することにより, 過渡解析が実施できるようにした. 熱雑音を発生するノイ ズ源は9段のPRBS発生回路, D/A コンバータ, ローパスフ ィルタ (LPF), 電圧制御発振器で構成した[9].9 段 PRBS のディジタル信号を D/A コンバータでアナログ信号に変 換し,LPF で想定帯域を規定することにより,帯域内でほ ぼ平坦な雑音源を生成できる. 電圧制御発振器では雑音の 実効値を可変とすることができ、常温で熱雑音に相当する 雑音量として 50 [ $\Omega$ ]負荷時に 0.29 [ $\mu$ V]を発生させ, D/A 変換器出力のアナログ信号に重畳した. 前置増幅回路 への入力電圧の大きさは、D/A 変換器の出力で調整した. 識別再生回路の出力を A/D 変換したパルスと,PRBS 発生 部のパルスを EX-OR 回路で比較し, さらに誤りパルス極性 判定部で符号"1"→"0"と誤ったのか,"0"→"1" と誤ったのかを判定し、識別しきい値の最適化を行った. また、クロック(CLK)は動作速度を決めるだけでな く,PRBS 発生部の出力パルスと識別再生回路出力を A/D 変換したパルスが完全に同期がとれるように, 識別再生回 路に入力する CLK の位相差を調整した.

回路シミュレーションにより 10,000 クロック分の疑似ランダム信号 (PRBS) による符号誤り検出を行い, BER が $10^{-4}$  以下となる条件下で, 一体化回路の消費電力が最小となる前置増幅回路の構成, 回路パラメータの最適化を検討した.

一体化回路の消費電力を評価するに当たり、識別再生回路に適用する CMOS D-FF は原理的に High レベル, Low レベルの定常状態では電流が流れないため電力消費は発生せず、レベルが変化する時の過渡状態においてのみ電力を消費し、平均消費電力は、CLK 数に依存して変動する. しかし、CLK 数の増加とともに平均消費電力は収束していき、1000 CLK 程度の平均をとれば十分であることが分っているため、テストパターンを 1000 CLK 分入力した時に、識別再生回路に接続された電源で消費される電力の平均値を識別再生回路の消費電力とした.

前置増幅回路の電源で消費される電力は CLK 数に依存 せず一定であり,前置増幅回路に接続された電源で消費さ れる電力を前置増幅回路の消費電力とした.前置増幅回路 と識別再生回路の消費電力を加えて一体化回路全体の消 費電力とした.

## 3. 検討結果と考察

### 3.1 ゲート幅に対する負帰還増幅回路の特性

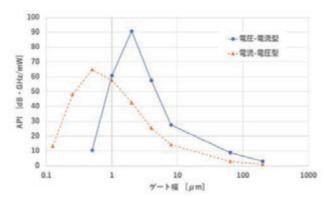

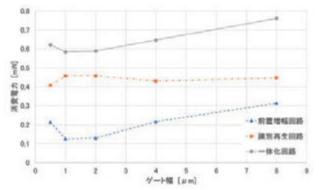

4 段構成の電圧-電流形帰還増幅回路及び電流-電圧型帰還増幅回路のゲート幅の各値に対して API が最大となる値 (極大値) をプロットした API のゲート幅依存特性を図 1 に示す。電圧-電流型帰還増幅回路ではゲート幅が  $2[\mu\,\mathrm{m}]$  の時に API がピークとなり,最大値は  $90[\mathrm{dB}\cdot\mathrm{GHz/mW}]$ であった。これに対し、電流-電圧型帰還増幅回路

ではゲート幅が  $0.5[\mu m]$ の時に API がピークとなり,最大値は  $66[dB \cdot GHz/mW]$ であった.これより 4 段構成において,電圧-電流型帰還増幅回路は,電流-電圧型帰還増幅回路の約 1.4 倍の API 最大値が得られることが分かった.

図1 負帰還増幅回路のAPIのゲート幅依存性

各ゲート幅において、API 極大値が得られたときの各特性パラメータの内訳を図2~図4に示す.

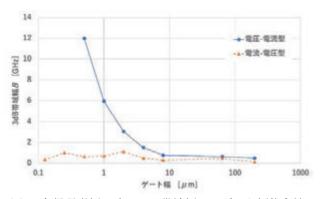

図 2 は特性パラメータを 3 d B 帯域幅 Bとしたときのゲート幅依存特性である. 電圧-電流形型還増幅回路では回路シミュレーションを実行したゲート幅  $0.5[\mu m]$ まではゲート幅を小さくするほど 3 d B 帯域幅が広くなり,ゲート幅  $0.5[\mu m]$ において 12[GHz]の値が得られた. これに対し電流-電圧型帰還増幅回路ではゲート幅  $2[\mu m]$ のときに 3 d B 帯域幅が最も広くなり 1.1[GHz]となった.

図2 負帰還増幅回路の3dB帯域幅Bのゲート幅依存性

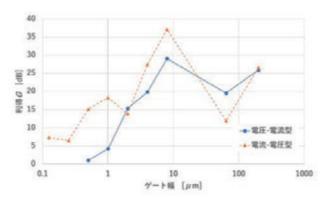

図3は特性パラメータを利得 G としたときのゲート幅依存特性である. どちらのタイプの負帰還増幅回路においても, ゲート幅が  $10[\mu m]$ で利得 G が最大となる傾向が見

図3 負帰還増幅回路の利得 Gのゲート幅依存性

られ,また,電流-電圧型の方が電圧-電流型よりも大きくなるという結果が得られた.

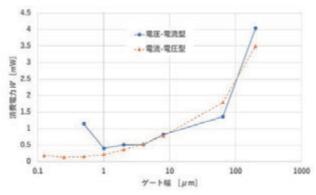

図4に特性パラメータを消費電力 W としたときのゲート幅依存特性を示す.電圧-電流型ではゲート幅  $1[\mu m]$ で最も低消費電力となり、0.4[mW]の値が得られた.電流-電圧型では、ゲート幅  $0.25[\mu m]$ までの範囲では、ゲート幅の減少とともに消費電力が低下し、図3の結果と合わせると、ゲート幅  $10[\mu m]$ までは、利得 G と消費電力 W はほぼトレードオフの関係にあることが明らかとなった.

図4 負帰還増幅回路の消費電力 Wのゲート幅依存性

表1 API 最大時の回路パラメータと特性パラメータ

| 電圧-電流型帰還增幅 | 回路(4段構) | 成、各段共通)     | 電流-電圧型帰還増幅回路(4段構成、各段共通) |      |             |  |

|------------|---------|-------------|-------------------------|------|-------------|--|

| 回路パラメータ    | - 16    | 単位          | 回路パラメータ                 | 植    | 単位          |  |

| 電源電圧VDD    | 3       | v           | 電源電圧V <sub>DD</sub>     | 3    | V           |  |

| ゲート電圧Vgg   | 600     | mV          | ゲート電圧Vgg                | 600  | mV          |  |

| 負荷抵抗RL     | 40      | kΩ          | 負荷抵抗RL                  | 80   | kΩ          |  |

| 帰還抵抗Re     | 70      | kΩ          | ピーキング抵抗R。               | 100  | Ω           |  |

| 帰還インダクタし。  | 4       | μН          | ピーキングコンデンサC。            | 0.1  | nF          |  |

| ゲート幅       | 2       | μm          | ゲート幅                    | 0.5  | μm          |  |

| 特性パラメータ    | - 4     | 単位          | 特性パラメータ                 | 値    | 単位          |  |

| 3dB帯域B     | 3.05    | GHz         | 3dB帯域B                  | 0.64 | GHz         |  |

| 電圧利得       | 15.3    | dB          | 電圧利得                    | 15.2 | dB          |  |

| 消費電力       | 0.514   | mW          | 消費電力                    | 0.15 | mW          |  |

| API最大值     | 90.9    | dB • GHz/mW | API最大值                  | 64.8 | dB • GHz/mW |  |

# 3.2 識別電圧に対する一体化回路の消費電力

#### 3.2.1 -40[dBm]入力時の消費電力

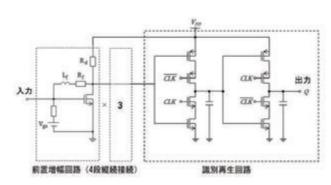

ディジタル受信回路への入力パワーを比較的小さい場 合を想定した入力パワー-40[dBm], これは  $50[\Omega]$ の抵抗 で電圧に変換すると 4.5[mV<sub>p-p</sub>]の入力電圧を仮定し,最も 大きい API が得られた, nMOSFET を適用した電圧-電流型 帰還増幅回路を4段縦続接続することにより,前置増幅回 路を構成した.この時,前置増幅回路の MOSFET のゲート幅 は、電圧-電流型帰還増幅回路の検討で最大の API 値が得 られた 2[μm]に設定した.これとクロックドインバータ 型 CMOS D-FF を識別再生回路として使用することにより, 図5に示す前置増幅回路と識別再生回路の一体化回路を 構成した.クロックドインバータ CMOS D-FF に適用した CMOSFET は、ゲート長 0.18[ $\mu$ m]、ゲート幅は識別再生回路 単体での検討時に使用した  $2[\mu m]$ に設定した[6]. クロ ックドインバータ D-FF は、一定のクロック周波数では動 作しない, いわゆるダイナミック動作型の D-FF である. 低 速度領域に適用するには速度調整用のコンデンサが必要 となるが、今回は 1Gbit/s の高速動作領域を前提としているため、このコンデンサは不要である.

図5 前置増幅回路と識別再生回路の一体化回路の構成

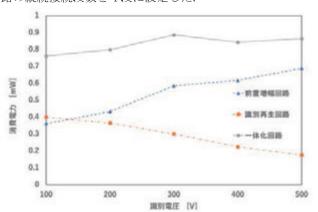

図6に識別再生回路の識別電圧に対する消費電力を前置増幅器単体,識別再生回路単体,一体化回路全体として示す.前置増幅回路の出力電圧が識別再生回路の識別電圧となる.識別再生回路では,識別不確定幅と呼ばれる識別電圧の最小値が存在し,それよりも小さい電圧を識別再生回路に入力すると,符号誤り率(BER)の所要値(本検討では10<sup>4</sup>以下)を得ることができなくなる.今回適用した識別再生回路の識別不確定幅は100[mV]であり,この時の前置増幅回路の所要電圧利得は27[dB]となる.今回は識別電圧が500[mV]まで検討しており,電圧利得は41[dB]まで必要である.この利得を得るため,電圧一電流型帰還増幅回路の縦続接続段数を4段に設定した.

図 6 識別電圧に対する一体化回路の消費電力特性 (-40[dBm]入力時)

図6より,識別再生回路単体では識別電圧を高く設定するほど消費電力が減少する.逆に前置増幅回路では識別電圧を低く設定するほど消費電力が減少する.識別電圧を最も低い識別不確定幅に設定した時,前置増幅回路の消費電力が最も小さくなり,一体化回路全体の消費電力も最も低減された.今回の検討では,前置増幅回路の消費電力の影響が最も大きく,この回路の消費電力の低減が一体化回路全体の低消費電力化に効果が高いことが判明した.

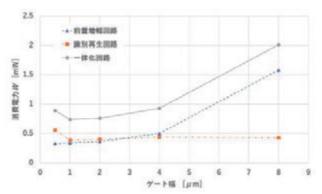

電圧-電流型帰還増幅回路単体では MOSFET のゲート幅が  $2[\mu m]$ の時,最も大きな API が得られ,このゲート幅を最初に一体化設計に適用したが,図 7に示すように,ゲート幅を変更した場合の一体化回路の消費電力特性についても検討を行った.ゲート幅が  $1[\mu m]$ の場合に一体化回路は最も低消費電力となったが,ゲート幅  $2[\mu m]$ の場合

との差はほとんどない。また、前置増幅回路の nMOSFET の ゲート幅のみを変更しており、ほぼ前置増幅回路の消費電力特性が一体化回路の消費電力特性に反映されている。 API 最大値を目標として設定したゲート幅と一体化回路 の低消費電力化を目標として設定したゲート幅は  $2[\mu m]$  から  $1[\mu m]$  へと若干の変化に留まった.

図7 ゲート幅に対する一体化回路の消費電力特性 (-40[dBm]入力時)

以上より一体化回路において最小の消費電力が得られた時の前置増幅回路及び識別再生回路の回路パラメータ及び特性パラメータを表2に示す.1Gbit/sの高速動作領域において、一体化回路の消費電力が最小となる時は、識別電圧は最も低い識別不確定幅である100[mV]となり、前置増幅回路と識別再生回路の消費電力はほぼ同等の値が得られた.

表2 一体化回路消費電力最小時の回路パラメータと 特性パラメータ (-40[dBm]入力時)

| 前置增幅回路(電圧-1        | 医流型4股积度。 | 各股共進) | 識別再生回路              |      |    |

|--------------------|----------|-------|---------------------|------|----|

| 回路パラメータ            | 催        | 単位    | 回路パラメータ             | 催    | 単位 |

| 電源電圧VDD            | 1.8      | V     | 電源電圧V <sub>DD</sub> | 1.8  | V  |

| ゲート電圧Vgg           | 600      | mV    | 動作速度調整コンデンサC        | 0    | nF |

| 負荷抵抗RL             | 10       | kΩ    | ゲート幅                | 2    | μm |

| 帰還抵抗R <sub>F</sub> | 50       | kΩ    | 識別電圧                | 100  | m۷ |

| 帰還インダクタレ。          | 10       | μН    |                     |      |    |

| ゲート幅               | 1        | μm    | 特性パラメータ             | 惟    | 単位 |

|                    |          |       | 消費電力                | 0.39 | mW |

| 特性パラメータ            | l litt   | 単位    |                     |      |    |

| 消費電力               | 0.34     | mW    |                     |      |    |

# 3.2.2 -20[dBm]入力時の消費電力

ディジタル受信回路への入力パワーを比較的大きい場合を想定した入力パワー-20 [dBm], 50 [ $\Omega$ ] の抵抗で電圧に変換すると 45 [mV<sub>p-p</sub>] の入力電圧を仮定し,電圧-電流型帰還増幅回路で構成される前置増幅回路の MOSFET のゲート幅は,電圧-電流型帰還増幅回路の検討で最大の API 値が得られた 2 [ $\mu$  m] に設定した.これとクロックドインバータ CMOS D-FF を識別再生回路として使用することにより,図 5 に示す前置増幅回路と識別再生回路の一体化回路を構成した.ただし,前置増幅回路の縦続接続段数は,必要とする電圧利得に応じて変更した.

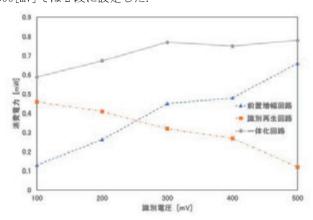

図8に識別再生回路の識別電圧に対する消費電力を前置増幅器単体,識別再生回路単体,一体化回路全体として示す.今回適用した識別再生回路の識別電圧の最小値である識別不確定幅は100[mV]であり,前置増幅回路の電圧利得は7[dB]以上となる.今回は識別電圧が500[mV]まで検討しており,電圧利得は21 [dB]まで必要である.この電圧利得を得るため,電圧-電流型帰還増幅回路の縦続接続

段数を,識別電圧が  $100[mV] \sim 400[mV]$ までは 1 段に設定, 500[mV]では 2 段に設定した.

図8 識別電圧に対する一体化回路の消費電力特性 (-20[dBm]入力時)

図8より,識別再生回路単体では識別電圧を高く設定するほど消費電力が減少する.逆に前置増幅回路では識別電圧を低く設定するほど消費電力が減少する. -40 [dBm]入力時と同様,識別電圧を最も低い識別不確定幅に設定した時,前置増幅回路の消費電力が最も小さくなり,一体化回路全体の消費電力も最も低減された.今回の検討では,識別電圧 100 [mV] 時では,一体化回路に占める消費電力において,識別再生回路が前置増幅回路の約 4.5 倍となった.これは,電圧利得の要求が 7 [dB]と小さく,前置増幅回路の縦続接続段数を1段に削減できたため,前置増幅回路の消費電力の大幅な削減が可能となったためである.

図9に示すように、ゲート幅を変更した場合の一体化回路の消費電力特性についても検討を行った。-40 [dBm]入力時と同様、ゲート幅が 1 [ $\mu$ m]の場合に一体化回路は最も低消費電力となったが、ゲート幅 2 [ $\mu$ m]の場合との差はほとんどない。また、前置増幅回路の nMOSFET のゲート幅のみを変更しており、ほぼ前置増幅回路の消費電力特性が一体化回路の消費電力特性に反映されている。API 最大値を目標として設定したゲート幅と一体化回路の低消費電力化を目標として設定したゲート幅は 2 [ $\mu$ m]から 1 [ $\mu$ m] へと若干の変化に留まった。

図 9 ゲート幅に対する一体化回路の消費電力特性 (-20[dBm]入力時)

以上より一体化回路において最小の消費電力が得られた時の前置増幅回路及び識別再生回路の回路パラメータ及び特性パラメータを表3に示す.1Gbit/sの高速動作領

域において一体化回路の消費電力が最小となる時は,識別電圧が最も低い識別不確定幅である 100 [mV] となり,前置増幅回路の消費電力は識別再生回路の消費電力の 28 [%] と小さな値が得られた.これは入力電圧が比較的大きいため前置増幅回路の所要電圧利得が小さく,1 段構成と回路規模を縮小できたためと考えられる.

表3 一体化回路消費電力最小時の回路パラメータと 特性パラメータ (-20[d Bm]入力時)

| 前置增幅回路(電)           | 王-電流型 1月 | 投構成) | 識別再生回路              |      |    |

|---------------------|----------|------|---------------------|------|----|

| 回路パラメータ             | - 101    | 単位   | 回路パラメータ             | 惟    | 単位 |

| を課電圧V <sub>DD</sub> | 1.8      | v    | 電源電圧V <sub>DD</sub> | 1.8  | V  |

| ゲート電圧Vgg            | 550      | mV   | 動作速度調整コンデンサC        | 0    | nF |

| 負荷抵抗RL              | 3        | kΩ   | ゲート幅                | 2    | μm |

| 帰還抵抗R <sub>F</sub>  | 50       | kΩ   | 識別電圧                | 100  | mV |

| 帰還インダクタし。           | 4        | μН   |                     |      |    |

| ゲート幅                | 1        | μm   | 特性パラメータ             | Mit  | 単位 |

|                     |          |      | 消費電力                | 0.46 | mW |

| 特性パラメータ             | 値        | 単位   |                     |      |    |

| 消費電力                | 0.13     | mW   |                     |      |    |

## 4. むすび

ディジタル受信機の主要要素である等化増幅回路と識別再生回路を一体化して、1Gbit/sの動作速度で最も低消費電力特性が得られる回路構成と回路パラメータを検討した。最初に等化増幅回路への適用を検討するため、電圧電流型、電流-電圧型の負帰還増幅回路について、利得、帯域幅、消費電力の3つの特性パラメータを一元的に評価することのできる性能指標 API を適用した。API は効率を表す性能指標である。nMOSFET のゲート幅を回路パラメータに加えて、増幅部および帰還部の各回路パラメータを最適化し、性能指標 API の最大値を求めた。この結果、電圧電流型の負帰還増幅回路が最も API が大きく、かつ1[GHz]を超える帯域幅を有しており、等化増幅機能を持つ前置増幅回路として最も有望であることが判明した。

次に、高速動作に優れたクロックドインバータ CMOS DFF をディジタル受信器の識別再生回路に適用した。検討した各種帰還増幅回路の内、最も API が大きくかつ1[GHz]程度以上の帯域幅が得られた電圧-電流形帰還増幅回路を、等化増幅機能を持つ前置増幅回路とした。識別再生回路と前置増幅回路を一体化し、1Gbit/s の高速動作が可能でかつ、一体化回路全体として最も低消費電力となる回路構成と回路パラメータを求めた。

一体化回路への入力が比較的小さい-40[dBm]入力時は,前置増幅回路の nMOSFET のゲート幅が  $1[\mu m]$ の時であり API 最大値から求めたゲート幅  $2[\mu m]$ と若干の変化に留まった。そして識別再生回路の識別電圧が,最小値である識別不確定幅の時に一体化回路の消費電力は最小となり,前置増幅回路と識別再生回路の消費電力はほぼ同等となった

一体化回路への入力が比較的大きい-20[dBm]入力時では,一体化回路が最も低消費電力となるのは,前置増幅回路のnMOSFETのゲート幅が $1[\mu m]$ の時でありAPI最大値から求めたゲート幅 $2[\mu m]$ と若干の変化に留まった。そして識別再生回路の識別電圧が最小値である識別不確定幅の時に,一体化回路の消費電力は最小となった。この時の前置増幅回路の消費電力は,識別再生回路の消費電力の28%と,-40[dBm]入力時より大幅に低減された。

以上により、高速動作に優れたクロックドインバータ CMOS D-FF と電圧-電流形負帰還増幅器から成る前置増幅 回路を一体化して検討を行い、1Gbit/s の高速動作領域で 最も低消費電力となる回路構成と回路パラメータを明らかにした.

# 参考文献

- [1] 高良秀彦, 大原拓也, 山本貴司, 山崎悦史, 犬塚史一, 高田篤, "マルチキャリア光発生技術および 1000 波長 WDM 伝送技術", 電子情報通信学会ソサイエティ大会, BCI-1-2, 2008.

- [2] 磯田曉, 水野隆之, 宮本裕, "マルチコア中継増幅光伝送システムにおける偏波多重モニタ光を用いたコア間クロストークの時間変動", 電子情報通信学会ソサイエティ大会, BC-10-20, 2018.

- [3] D. Evans, CISCO White Paper, 2011.

- [4] 大川典男, "小信号電圧増幅回路の帯域利得特性・消費電力に関する性能指標", 電子情報通信学会論文誌 Vol. J92-C No. 7, 2009.

- [5] 大川典男,一澤春希, "各種負帰還増幅回路の性能指数 API を用いた性能比較", 東京都立産業技術高等専門学校研究紀要第 15 号, p.64~p.71,2021.

- [6] 一澤春希,大川典男, "クロックドインバータ型 D-FF を用いた通信用受信回路における低消費電力化の検討",電子情報通信学会東京支部学生会 第 26 回研究発表会,講演番号 100, 2021.

- [7] 大川典男,小林遥希, "トランスファーゲート、クロック電流制御を適用した識別再生回路の性能評価", 東京都立産業技術高等専門学校研究紀要第 14 号, p. 45~p. 50, 2020.

- [8] 大川典男,小林遥希,"前置増幅回路・識別再生回路 の一体化設計による受信機の低消費電力化の検討", 東京都立産業技術高等専門学校研究紀要第 12 号, p.41~p.46,2018.

- [9] 大川典男,小林遥希,大島慶太,"識別再生回路の応答速度・消費電力・識別不確定幅に関する性能評価", 東京都立産業技術高等専門学校研究紀要第 11 号, p.59~p.64,2017.