# トランスファーゲート、クロック電流制御を適用した識別再生回路の性能評価

Performance Evaluation of Decision Circuits Employing Transfer Gates and Clock Current Control

大川 典男1

小林 遥希2

Norio Ohkawa

Haruki Kobayashi

#### Abstract:

In performance evaluation of regeneration circuits which are the component of transmission receivers, it is necessary to consider not only power consumption and operating speed, but also decision voltage representing input voltage at which the specified bit error rate can be obtained. In order to apply them as the regeneration circuits, newly devised D-FFs, conventional master-slave D-FFs, and clocked inverter type D-FFs were compared and evaluated employing performance index DPI which was considered power consumption, clock operating speed, and decision voltage. In the front-end section of the newly devised D-FFs, when signal data was in transient state, it was turned ON / OFF with a clock at twice the speed so that current through the differential pair was OFF by the clock current control technique. Also, in the D-latch section, transfer gates were applied to hold data regardless of signal data rate. Comparing the devised circuits and conventional circuits shows that the DPI values of the devised circuits are relatively small fluctuation regardless of operation speed, but in the conventional circuits, DPI values are proportional to operation speed. We clarified that the devised circuits have better DPI values than the conventional circuits in low-speed operation region, and operate up to higher speed.

### Keywords:

Performance index, Decision voltage, Low-power consumption, Transfer gate, Clock current control

### 1. まえがき

波長多重技術を初めとする光通信技術の急速な進展により、光ファイバ1本当たり100波長程度のシステムが商用化されており、1000波長の伝送実験[1]にも成功している。光ファイバ1本当たり、波長数に相当する受信器が必要となるため、光通信に適用される受信器は高速化のみならず低消費電力化が重要な課題となっている。また、今後急速な進展が期待されるIoT (Internet of things)用のネットワークデバイスは、2020年には世界で500億個に達し、最終的には毎年1兆個を超えるセンサーネットワークデバイスを活用する時代が到来すると予想されている[2]。ワイヤレスセンサーネットワークでは、管理コストの観点からバッテリーレスで動作する送受信器が強く要望されており、これを実現するために搬送波や環境電波からの給電で駆動できるレベルまで低消費電力化する必要がある。

ディジタル受信器は一般的に 3R 機能(等化増幅、タイミング抽出、識別再生)を有している。アナログ回路である等化増幅回路では、帯域、利得、消費電力を一元的に評価する性能指標 API を提案し[3]、様々な増幅回路の性能評価を行ってきた。これに対し、識別再生回路は雑音や波形歪が付加された信号の符号を判定し再生する機能を持ち、D-FF などのディジタル回路で構成されている。ディジタル回路の性能評価には、高速化及び低消費電力化を一元的に評価する性能指標として、PD 積(消費電力とゲート遅延時間の積)や ED 積 (PD 積とゲート遅延時間の積)などの性能指標がある[4]。しかし、これらの性能指標では一般的

なディジタル回路単体としての評価は可能であるが、ディジタル受信器全体から見た、識別再生回路としての要求性能を評価するには十分ではない。例えば、識別再生回路への入力信号電圧振幅が低減できれば、前置される等化増幅回路の利得が低減でき、受信器全体の低消費電力化につながる。

消費電力とクロック(CLK)動作速度にさらに、識別再生回路の前段の等化増幅回路の要求利得の指標となる、規定の符号誤り率以下で動作可能な入力電圧である識別電圧を特性パラメータに加えた性能指標 DPI を提案した[5]。識別再生回路の低消費電力化、及び高速化を図るために、トランスファーゲート (TG) 及び CLK 電流制御 (CC) を適用した CMOS マスタースレーブ (MS) 型 D-FF を考案し、識別再生回路としての性能を DPI を用い、従来の MS 型 D-FF、クロックドインバータ型 D-FF[6]と比較評価することにより、その特性と適用性を明らかにした。

# 2. 性能指標の概要

TG、CLK-CC を適用した CMOS MS 型 D-FF による識別再生 回路の性能を評価するため、特性パラメータである消費電力、CLK 動作速度、識別電圧を一元的に評価する性能指標 DPI を適用した。最初に性能指標の定義を示し、次に各特性パラメータの評価方法について述べる。

# 2.1 性能指標 DPI の定義

識別再生回路の性能指標 DPI (Decision circuit Performance Index) を、式(1)のように定義した[5]。

<sup>&</sup>lt;sup>1</sup> 東京都立産業技術高等専門学校ものづくり工学科電子情報工学コース

<sup>&</sup>lt;sup>2</sup> 東京都立産業技術高等専門学校創造工学専攻電気電子工 学コース 在学

$$DPI = \frac{20 \cdot \log(V_{\rm DD}/X) \cdot F}{W} \quad [(dB \cdot Hz)/W]$$

(1)

ここで、W は消費電力 [W]、F は CLK 動作速度 [Hz]、X は識別電圧 [V]である。  $(V_{DD}/X)$  とすることにより最大出力電圧である電源電圧  $V_{DD}$  [V] に対する入力電圧余裕度を表すことができる。さらに、 $20\cdot \log(V_{DD}/X)$  とすることによりこれをデシベル表示とした。これは、等化増幅回路の性能指標として API [3] を提案しており、API の特性パラメータである利得がデシベル表示となっているため、それとの接続性を考慮したためである。消費電力、CLK 動作速度と入力電圧余裕度の特性パラメータを一元的に評価したものが DPI となる。DPI は単位消費電力当たりの所要入力電圧・動作速度積、つまり効率を表す指標であり、DPI が大きいほど識別再生回路の性能が優れていることを示す。

### 2.2 識別電圧の評価方法

識別電圧は、識別再生回路として用いられる D-FF の CLK 入力に規定電圧の CLK 信号を入力し、データ (DATA) 入力 への信号電圧を調整した時、D-FF 出力信号の符号誤り率 (BER)が  $10^{-4}$ 以下を満たす DATA 入力電圧と定義した。このため、識別電圧は一般的に識別不確定幅と呼ばれる最小値から最大値に相当する電源電圧  $V_{DD}$  までの範囲を持つ。

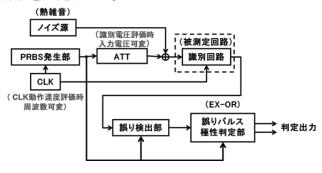

図 1 に識別電圧を求めるための評価系を示す[5]。この 評価系では、PRBS 発生部からのテストパターン信号をπ型 不平衡アッテネータ(ATT)内部の抵抗値を変えて可変減 衰させることにより、D-FF への DATA 入力信号の電圧を調 整した。減衰させた DATA 入力信号には常温での熱雑音に 相当するノイズを重畳した。誤判定を防ぐため、位相差を 調整したクロック信号を識別再生回路に入力し、回路シミ ュレーションにより全体として 10,000 クロック分の疑似 ランダム信号 (PRBS) の識別再生を行った。識別再生後の D-FF の出力信号と PRBS 発生部からのテストパターンを誤 り検出部 (EX-OR) でパルス比較することにより、符号誤 りを検出し、BER が 10<sup>-4</sup> 以下を確保できる入力信号電圧の 範囲を求めた。CMOS 型 D-FF の消費電力は識別電圧依存性 があり、識別電圧を減少させていくと、定常状態よりも過 渡応答の状態となる時間的割合が増加し、消費電力が増加 する傾向にある。このため、DPI が最も大きくなるように 識別電圧を設定した。

図1. 識別電圧の評価系

テストパターン発生には回路シミュレータの収束性を考慮して7段のPRBSを用いた。PRBS発生回路は、D-FFを縦続接続して構成したシフトレジスタとEX-ORを組み合わせることで最大長周期系列を発生する符号器として実現でき

るが、回路シミュレータのライブラリでは D-FF はデジタル信号として出力されるので、DA コンバータを介し、電圧振幅を可変とすることが可能なアナログ信号に変換することにより、識別電圧を求めるための過渡解析が実施できるようにした。

熱雑音を発生するノイズ源は 9 段の PRBS 発生回路、DA コンバータ、ローパスフィルタ(LPF)、電圧制御発振器で構成した。PRBS 発生回路のディジタル出力を DA コンバータでアナログ出力に変換し、LPF で想定帯域を規定することにより、帯域内でほぼ平坦な雑音源として扱うことが可能である。電圧制御発振器では雑音の実効値を可変とすることができ、常温で熱雑音に相当する雑音量として  $(0.29 \ [\mu V]@50 \ [\Omega])$  を発生させた。

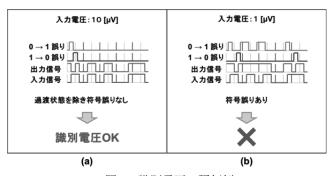

図 2 に識別電圧の評価例を示す。図 2 -(a)のように識別再生回路への DATA 入力電圧が  $10[\mu V]$ の時はシミュレーション開始直後の過渡状態を除き、符号誤りが生じていないため、この入力電圧は識別電圧の範囲内であるが、図 2 -(b)のように DATA 入力電圧が  $1[\mu V]$ の時は、シミュレーション開始直後の過渡状態を過ぎても符号誤りが生じており、識別電圧範囲外であることが判る。

図 2. 識別電圧の評価例

# 2.3 消費電力の評価方法

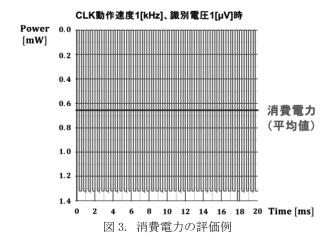

CMOS 型 D-FF は過渡応答時に電力を消費するため、消費電力は、回路の動作速度に依存する。このため、テストパターンを 1000 CLK 分入力した時に、電源で消費される電力の平均値をその動作速度における回路の消費電力とした。

図 3 に CMOS 型 D-FF の消費電力の評価例を示す。この例では定常状態の 0[mW] から過渡状態において最大 1.33[mW]まで変動しており、平均値の 0.66[mW] を CMOS 型 D-FF 回路の消費電力とした。

### 2.4 CLK 動作速度の評価方法

CLK 動作速度は、D-FF の DATA 入力及び CLK 入力に規定の信号電圧を入れ、CLK 信号速度を上昇させた時に、D-FF が規定の BER (10<sup>-4</sup>) 以下で動作する上限値を CLK 動作速度と定義した。CLK 動作速度の求値には、図 1 に示す識別電圧の求値と同一の評価系が適用できる。クロック動作速度を用いることにより DPI は、等化増幅回路の性能指標である API と同一の次元 [(dB・Hz)/W]を持ち、識別再生回路だけでなく受信器全体としての一元的な評価に繋げることができる。

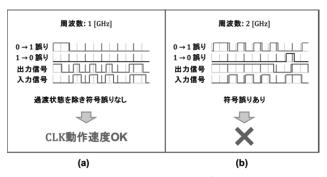

図4にCLK動作速度の評価例を示す。図4-(a)のように識別再生回路へのCLK周波数が1[GHz]の時はシミュレーション開始直後の過渡状態を除き、符号誤りが生じていないため、この周波数はCLK動作範囲内であるが、図4-(b)のようにCLK周波数が2[GHz]の時は、回路シミュレーション開始直後の過渡状態を過ぎても符号誤りが生じており、CLK動作範囲外であることが判る。

図4. 識別電圧の評価例

# 3. 識別再生回路の構成

# 3.1 TG 及び CLK-CC を適用した CMOS-MS 型 D-FF

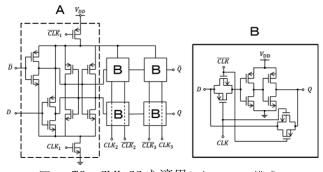

図 5 に、新たに考案し、DPI による性能評価を行った、トランスファーゲート (TG)、クロック (CLK) 電流制御 (CC) を適用した識別再生回路の構成をを示す。Aのフロントエンド部では高感度化による最小識別電圧の低減と低消費電力化を両立させるため、CMOS 差動対に流れる電流を CLK により ON/OFF する構成とした。CMOS 構成は、データが Low、あるいは High の定常状態では電力を殆ど消費せず、Low と High が変化する過渡状態において電力消費が発生する。A での CLK 速度は信号データ速度の 2 倍とし、信号データの過渡状態時に  $V_{DD}$  からグランドまでの電流経路が OFF となるように信号データと CLK の位相を調整した。動作速度に

図 5. TG、CLK-CC を適用した D-FF の構成

よらず信号データを保持するため、フロントエンド部の差動対の出力のそれぞれに、Bに示すような TG を適用した CMOS 構成の D-ラッチを 2 段縦続接続することにより、D-FF を構成した。適用する CMOSFET はゲート長  $0.18[\mu m]$ 、電流量に応じてゲート幅を  $4[\mu m]\sim 16[\mu m]$ に設定した。

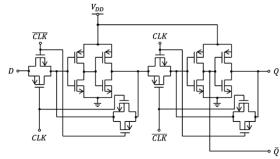

### 3.2 TG を適用した CMOS-MS 型 D-FF

図5のTG、CLK-CCを適用したD-FFではAのフロントエンド部で高感度化を図り、より小さな識別電圧の要求にも対応可能である。しかし、フロントエンド部では、CLK-CCを適用して通常よりも削減しているものの、消費電力が発生する。識別再生回路の低消費電力化を主眼として、フロントエンド部を持たず、TGとCMOS構成を組み合わせたDーラッチを2段縦続接続して、よりシンプルなMS型のD-FFを考案した。その構成を図6に示す。図5のBに示すD-ラッチを適用したシンプルな構成であり、TGにより保持部のデータ書き換え、データ保持の制御を行っている。

図 6. TG を適用した D-FF の構成

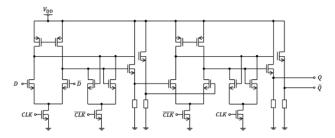

# 3.3 従来の MS 型 D-FF

考案した D-FF との性能比較を行うため、図 7 に示すように、従来型 D-FF として、nMOS の差動対によりデータの保持を行う D ラッチを 2 段縦続接続することにより MS 型の D-FF を構成した。CMOS 構成の差動対ではないため、CLKが ON の時は、電流を消費するが、動作速度によらずデータ保持が可能な構成となっている。

図 7. 従来型 MS 型 D-FF の構成

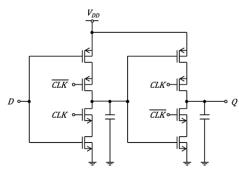

### 3.4 クロックドインバータ型 D-FF

考案した D-FF との性能比較を行うためのもう一つ別の種類の D-FF として、クロックドインバータ型 D-FF の構成 [6]を図 8 に示す。シンプルな CMOS インバータを CLK で電流制御した D ラッチを 2 段縦続接続して D-FF を構成している。100 [MHz] を越える高速度領域ではデータ保持は可能であるが、それ以下の中低速度領域ではそのままではデータを保持することができない、いわゆるダイナミック型と呼ばれる構成となる。中低速度領域におけるデータを保持

できるようにするためには、D ラッチの出力と並列にコンデンサを挿入し、動作速度に合わせた適正な容量を選択する必要がある。

図 8. クロックドインバータ型 D-FF の構成

# 4. 識別再生回路の性能評価

新たに考案した TG 及び CLK-CC を適用した CMOS-MS 型 D-FF 及び、TG を適用した CMOS-MS 型 D-FF の性能を評価するため、性能指標 DPI を用いて、従来の MS 型 D-FF とクロックドインバータ型 D-FF との比較を行った。回路シミュレーションには、収束性に優れた SPICEIII をベースとし、短ゲート長 MOSFET デバイスモデルや PSPICE のトランジスタモデルにも対応可能な SIMetrix を用いた。

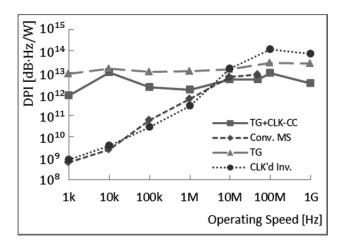

#### 4.1 動作速度と性能指標 DPI に関する評価

図9に各種 D-FF の動作速度に対するDPIを示す。今回検討した、トランスファーゲートとクロック電流制御を組み合わせたCMOS-マスタースレーブ型D-FFをTG+CLK-CCとして、トランスファーゲートのみを用いたCMOS-マスタースレーブ型D-FFをTGとして、また、比較検討用に従来のマスタースレーブ型D-FFをConv.MSとして、クロックドインバータ型D-FFをCLK'dInv.として表している。CLK'dInv.はダイナミック型のD-FFであるため、そのままでは中低速動作領域でのデータ保持の機能を有していないが、各ラッチの出力に並列に挿入したコンデンサの電荷の充電により、データ保持の機能を持たせた。しかし、コンデンサに充電した電荷は容量が小さ過ぎると時間とともすぐ放電してしまい、必要な保持時間が確保できなくなる恐れが

図 9. 各種 D-FF の動作速度に対する DPI

ある。また、容量が大き過ぎると高速動作に充放電が追従できなくなるため、動作速度毎に適正な容量のコンデンサを使用する必要がある。

TG+CLK-CC、TG では、動作速度に対して DPI の変化は比 較的小さいが、比較用の Conv.MS、CLK'd Inv.では動作速 度とともに比例して DPI が上昇する。これは、検討回路で ある、TG+CLK-CC、TG は CMOS 型であり、電力消費は信号デ ータの過渡状態時のみ発生する。CMOS 型は定常状態では原 理的に電力を消費せず、消費電力は動作速度に比例して増 加し、DPI の動作速度を消費電力で除した項が一定となる ため、DPI の変化が小さくなったと考えられる。これに対 し、比較用の Conv. MS では消費電力は動作速度によらず、 CLK'd Inv. も消費電力の動作速度に対する依存性が小さい ため、DPI は低速ほど減少すると考えられる。これより検 討回路である、TG+CLK-CC、TG は低速でも効率が低下しな いという特徴が得られ、数 MHz 以下の中低速動作領域では、 比較用回路に対し、効率が優れていることが明らかとなっ た。なお、Conv. MS では最大動作速度が 50 [MHz] であり、 検討回路である TG+CLK-CC、TG の 4[GHz]や CLK'd Inv.の 6[GHz]と比較して十分な高速動作が得られなかった。

# 4.2 識別電圧と消費電力に関する評価

性能指標 DPI は識別電圧 Xが特性パラメータとなっており、この値が小さいほど前置する増幅回路の利得が低減でき、この観点からは、識別不確定幅と呼ばれる識別電圧の最小値まで、識別電圧 Xを低減することが望ましい。

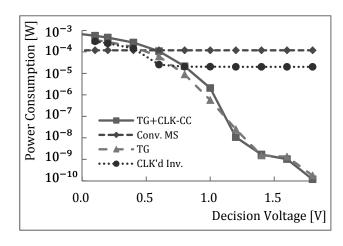

図 10 に低速動作速度として、10 [kHz]での識別電圧に対する消費電力の関係を示す。CMOS 構成の TG+CLK-CC と TGでは、Xの低減とともに消費電力 Wが増加する傾向がある。これは、Xを低く設定すると、信号の定常状態に対する過渡状態の割合が増加し、電流が流れ続く割合が増加するので電力を消費するためであると考えられる。これに対し、Conv. MS はこの影響を全く受けず、CLK'd Inv. については、CMOS 構成のインバータを CLK 電流制御しており、それと記憶保持用コンデンサの充放電との関係から、低識別電圧の領域では、Xの増加とともに Wが低減されるが、ある程度以上の識別電圧の領域では、低速動作領域に適合した大容量の記憶保持用コンデンサへの充放電量が増加するため、Wはある程度以下には下がらなくなったためと考えられる。

図 10. 動作速度 10[kHz]での識別電圧に対する消費電力

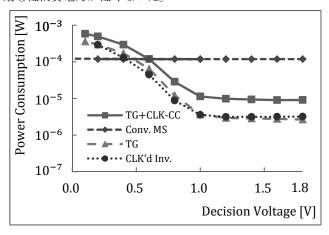

図 11 に中速動作速度として、10[MHz]での識別電圧に対する消費電力の関係を示す。TG+CLK-CC と TG では、識別電圧の増加とともに消費電力が低減されるが、識別電圧を1[V]以上にしても W は下がらなくなる。これは、動作速度が速くなり、ある程度以下に過渡状態の割合を減らすことができなくなったためと考えられる。また、CLK'd Inv.については、適正な記憶保持用コンデンサの容量が小さくなり、コンデンサの充放電の影響が低減されるため、10[kHz]のときよりも高い識別電圧まで消費電力が低減されるようになったと考えられる。TG と CLK'd Inv.では、識別電圧に対して、同等の消費電力特性が得られた。また、Conv. MS については動作速度や識別電圧の影響を全く受けず一定値を保っており、識別電圧が 0.5[V]未満の場合では、最も低消費電力が低くなった。

図 11. 動作速度 10 [MHz] での識別電圧に対する消費電力

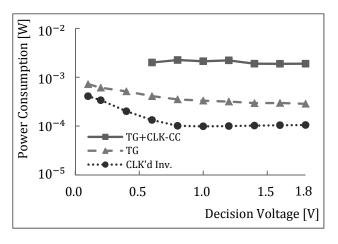

図 12 に高速動作速度として、1 [GHz]での識別電圧に対する消費電力の関係を示す。Conv. MS はこの動作速度では所要の BER (10<sup>-4</sup>)を確保することができなかった。この動作領域では、CLK'd Inv. が識別再生回路単体として最も低消費電力であり、TG がそれに次ぎ、回路構成がシンプルな程、消費電力が小さい結果となった。識別電圧が 0.8[V]以下では識別電圧の減少とともに、両者の差は縮まっていく。識別電圧が低くなるほど前段の増幅回路の利得は小さくて済み、増幅回路の低消費電力化を図ることが可能であ

図 12. 動作速度 1[GHz]での識別電圧に対する消費電力

るが、Conv. MS を除く識別再生回路単体では識別電圧の低下とともに消費電力が増加する傾向にあることが図 10~図 12 からわかる。前段の増幅回路と合わせて、受信回路全体としての低消費電力化を図るために最適な識別電圧の設定法については、今後の課題である。

識別再生回路に適用するための各種 D-FF について、回路シミュレーションによる性能比較を表1に示す。1[GHz] 以上の高速動作領域では、CLK'd Inv.が DPI、最大動作速度、消費電力において最も優れているという結果となった。これより CLK'd Inv.は、光伝送などの大容量通信用回路に適した構成であると言える。

10[kHz]以下の低速動作領域では、TG が消費電力において最も優れ、TG+CLK-CC が識別電圧最小値において最も優れているという結果となった。IoT に適用されるワイヤレスセンサーネットワーク用送受信回路では、バッテリーレス動作に対する強い要望から、低消費電力動作は最重要な特性パラメータであり、この動作速度領域でのアプリケーションとして、TG が最も適した回路構成であると言える。

10[MHz]程度の中速動作領域では、TG が低速動作領域と同様、消費電力において最も優れ、Conv. MS が識別電圧最小値において最も優れているという結果となった。この動作領域でのアプリケーションとして、動作速度、消費電力のバランスを考慮したモバイル機器用には、TG が最も適した構成であると言える。

|                              | TG+CLK-CC | TG        | Conv.MS  | CLK'd Inv |

|------------------------------|-----------|-----------|----------|-----------|

| DPI 最大値<br>[dB•Hz/W]         | 1.00E+13  | 2.79E+13  | 8.02E+12 | 1.17E+14  |

| DPI MAX<br>時の動作速度<br>[Hz]    | 100k      | 100M      | 50M      | 100M      |

| 最大動作速度<br>[Hz]               | 4G        | 4G        | 50M      | 6G        |

| 消費電力<br>[W]<br>@10kHz        | 117p      | 1.75p     | 118 μ    | 20.0 μ    |

| 消費電力<br>[W]<br>@10MHz        | $9.05\mu$ | $2.65\mu$ | 118 μ    | 3.19 μ    |

| 消費電力<br>[W]<br>@1GHz         | 1.879m    | 286 μ     |          | 105 μ     |

| 識別電圧<br>最小値<br>[V]<br>@10kHz | 10 μ      | 100m      | 300 μ    | 100m      |

| 識別電圧<br>最小値<br>[V]<br>@10MHz | 100m      | 100m      | 400 μ    | 100m      |

| 識別電圧<br>最小値<br>[V]<br>@1GHz  | 600m      | 100m      |          | 100m      |

表 1. 各種 D-FF の性能比較

# 5. まとめ

ディジタル受信回路の主要構成要素である識別再生回路に適用するため、トランスファーゲート(TG)、及び、TG とクロック電流制御(CLK-CC)の両者(TG+CLK-CC)を用いた CMOS マスタースレーブ(MS)型 D-FF を考案し、従来の MS 型(Conv. MS)の D-FF やダイナミック型で高速性を

指向したクロックドインバータ型(CLK'd Inv.)の D-FF との性能比較を行った。総合的な性能比較を行うため、収束性に優れ短ゲート長 MOSFET デバイスモデルにも対応可能な SIMetrix により回路シミュレーションを実施し、特性パラメータである消費電力、CLK 動作速度、識別電圧を求め、それらの特性パラメータを一元的に評価する性能指標DPI を適用した。また、各動作毎に識別電圧に対する消費電力の比較を行った。

動作速度と DPI に関する評価において、TG+CLK-CC、TGでは、動作速度に対して DPI の変化は比較的小さいが、比較用の Conv. MS、CLK'd Inv. では動作速度とともに比例して DPI が上昇する。これは、検討回路である、TG+CLK-CC、TGでは CMOS 型であり、電力消費は信号の過渡状態時に発生し、定常状態では原理的に電力を消費しないため、消費電力は動作周波数に比例して増加し、DPI の動作速度を消費電力で除した項が一定となるためであると考えられる。これに対し、比較用の Conv. MS では消費電力は動作速度によらず、CLK'd Inv. も消費電力の動作速度に対する依存性が小さいため、DPI は低速ほど減少すると考えられる。これより検討回路である、TG+CLK-CC、TG は低速でも効率が低下しないという特徴が得られ、数 MHz 以下の中低速動作領域では、比較用回路に対し、効率が優れていることが明らかとなった。

低速動作速度として、10 [kHz]での識別電圧に対する消費電力の比較では、CMOS 構成の TG+CLK-CC と TG では、識別電圧 Xの低減とともに消費電力 Wが増加する傾向がある。これは、X を低く設定すると、信号の定常状態に対する過渡状態の割合が増加し、電流が流れ続く割合が増加するので電力を消費するためであると考えられる。これに対し、Conv. MS はこの影響を全く受けず、CLK'd Inv. については、CMOS 構成のインバータを CLK 電流制御しており、それと記憶保持用コンデンサの充放電との関係から、低識別電圧の領域では X の増加とともに Wが低減されるが、ある程度以上の識別電圧の領域では、低速動作領域に適合した大容量の記憶保持用コンデンサへの充放電量が増加するため、W はある程度以下には下がらなくなったためと考えられる。

中速動作速度として、10 [MHz] での識別電圧に対する消費電力の比較では、TG+CLK-CC と TG では、識別電圧の増加とともに消費電力が低減されるが、識別電圧を 1 [V] 以上にしても W は下がらなくなる。これは、動作速度が速くなり、ある程度以下に過渡状態の割合を減らすことができなくなったためと考えられる。また、CLK'd Inv. については、適正な記憶保持用コンデンサの容量が小さくなり、コンデンサの充放電の影響が低減されるため、10 [kHz] のときよりも高い識別電圧まで消費電力が低減されるようになったと考えられる。TG と CLK'd Inv. では、識別電圧に対して、同等の消費電力特性が得られた。また、Conv.MS については動作速度や識別電圧の影響を全く受けず一定値を保っており、識別電圧が 0.5 [V] 未満の場合では、最も消費電力が低くなった。

高速動作速度として、1[GHz]での識別電圧に対する消費電力のの比較において、Conv.MS はこの動作速度では所要の BER ( $10^{-4}$ ) を確保することができなかった。この動作領域では、CLK'd Inv. が識別再生回路単体として最も低消費電力であり、TG がそれに次ぎ、回路構成がシンプルな程、消費電力が小さい結果となった。識別電圧が 0.8[V]以下で

は識別電圧の減少とともに、両者の差は縮まっていく。前段の増幅回路と合わせて、受信回路全体としての低消費電力化を図るために最適な識別電圧の設定法については、今後の課題である。

1[GHz]以上の高速動作領域では、CLK'd Inv.が DPI、最大動作速度、消費電力において最も優れているという結果となり、この回路構成は、光伝送などの大容量通信用回路に適した構成であると言える。

10[kHz]以下の低速動作領域では、TG が消費電力において最も優れ、TG+CLK-CC が識別電圧最小値において最も優れているという結果となった。IoT に適用されるワイヤレスセンサーネットワーク用送受信回路では、バッテリーレス動作に対する強い要望から、低消費電力動作は最重要な特性パラメータであり、この動作速度領域でのアプリケーションとして、TG が最も適した回路構成であると言える。

10[MHz]程度の中速動作領域では、TG が低速動作領域と同様、消費電力において最も優れ、Conv. MS が識別電圧最小値において最も優れているという結果となった。この動作領域でのアプリケーションとして、動作速度、消費電力のバランスを考慮したモバイル機器用には、TG が最も適した構成であると言える。

以上より、識別再生回路に適用するための各種 D-FF の性能比較を行い、考案した D-FF の特性と適用性について明らかにした。

### 参考文献

- [1] 高良秀彦、大原拓也、山本貴司、山崎悦史、犬塚史一、高田篤、"マルチキャリア光発生技術および 1000 波長 WDM 伝送技術"、電子情報通信学会ソサイエティ大会、BCI-1-2、2008.

- [2] D. Evans, CISCO White Paper, 2011.

- [3] 大川典男、"小信号電圧増幅回路の帯域利得特性・消費電力に関する性能指標、"電子情報通信学会論文誌 Vol. J92-C No. 7、2009.

- [4] 岩田穆, "CMOS 集積回路の基礎, "科学技術出版, 東京, 2003

- [5] 大川典男、小林遥希、大島慶太、"識別再生回路の応答速度・消費電力・識別不確定幅に関する性能評価、" 東京都立産業技術高等専門学校研究紀要 11号、2017.

- [6] 鈴木成人、関口貴之、天川修平、石原昇、益一哉、 "クロックドインバータ型 D-FF による MUX/DEMUX の研究"、電子情報通信学会総合大会、C-12-58、2010.