# PSpice 電子回路シミュレータに適用可能な GaAsMESFET デバイスモデルの作成

GaAsMESFET device modeling for the PSpice electronic circuit simulators

大川 典男1

清水 英貴2

鈴木 智大3

Norio Ohkawa

Hideki Shimizu

Tomohiro Suzuki

#### Abstruct

Recently, a role of the electronic circuit simulation in the electronic circuitry design becomes more important. In the design employing circuit simulation, the change of the circuit parameters is easy because it is not fear to destroy circuit elements by a mistake like a design employing the measurement of the manufactured circuit. In addition, there is a merit to be able to demand the most suitable circuit parameter values comparatively in a short time.

PSpice is a popular electronic circuit simulator possessed economy and a high versatility but the GaAsMESFET.

PSpice is a popular electronic circuit simulator possessed economy and a high versatility, but the GaAsMESFET device model which is one of the high-speed transistors is not available in this simulator. The developed device model for PSpice is based on the equivalent GaAsMESFET circuit model of TSpice for mainframes, more, which is raised characteristic curve-fitting between the simulated curves and the measured ones, is reported in this study.

キーワード: GaAsMESFET、カーティスモデル、PSpice、特性パラメータ、性能指標 API (GaAsMESFET, Curtice Model, PSpice, Characteristic parameters, Performance index API)

# 1. まえがき

光通信システムにおける光受信回路は、高速化だけでなく、同時に低消費電力化を図ることが重要な課題となってきている。この課題を検討するに当り、電子回路設計における回路シミュレーションの役割が近年、ますます重要となってきている。回路シミュレーションによる設計では、試作回路の測定による設計のように誤って回路素子を破壊する恐れがないだけでなく、回路パラメータの変更が容易であり、最適な回路パラメータ値を比較的短時間で求めることができるというメリットがある。

GaAsMESFETは、高速素子として従来より使用されているSiバイポーラトランジスタと比較して、自由電子の移動度及び飽和ドリフト速度が高い、だ雑音が小さいなど高速特性に優れたトランジスタであり、高速かつ低消費電力に優れた光受信回路を実現するためのトランジスタとして有力な候補のひとつである。

PSpiceは経済的で汎用性の高い電子回路シミュレータであるが、GaAsMESFETデバイスモデルは標準ライブラリに登録されていない。従来、大型計算機用に開発された電子回路シミュレータTSpice用としてカーティスモデル[1]に基づいたGaAsMESFETデバイスモデルが存在するが、トランジスタの線形領域において、ゲートーソース間電圧 $V_{GS}$ や

ドレイン-ソース間電圧V<sub>IS</sub>が広い範囲に亘ると、モデル値と実測値とが乖離することが指摘されている[2]。

今回作成したGaAsMESFETデバイスモデルは、等価回路が簡単なカーティスモデルをベースとしているが、トランジスタの特性パラメータであるLAMBDA、GAMMA、 $VTOをV_{CS}$ の多項式として表わし、また $BETAeV_{CS}$ を変数とした指数関数として表現することにより、ドレイン電流Idに関して $V_{CS}$ 及び $V_{DS}$ の広い範囲に亘り、実測値とのカーブフィッテングを高めることができ、PSpice上で使用可能であることを確認したので報告する。

# 2. GaAsMESFET 等価回路とフィッテイング

# 2.1. DC カーブフィッテイング

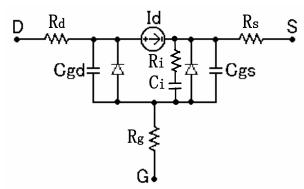

回路シミュレーションによる設計では、FFT などのトランジスタの動作バイアス点は等価回路モデルに基づいて決定される。図1にカーティスモデルに基づいた GaAsMESFET 等価回路を示す。DC カーブフィッテイングではこの等価回

図1. GaAsMESFET の等価回路

<sup>&</sup>lt;sup>1</sup>東京都立産業技術高等専門学校ものづくり工学科電子情報 工学コース、教授

<sup>&</sup>lt;sup>2</sup>東京都立工業高等専門学校電子情報工学科卒、現在、日本 空港テクノ株式会社施設管理部勤務

<sup>&</sup>lt;sup>3</sup>東京都立工業高等専門学校電子情報工学科卒、現在、株式 会社KDDIテクニカルエンジニアリングサービスオプティカ ル建設部勤務

路中のCi、Cgs、Cgdをオープンとして扱う。

GaAsMESFETはディプレッション形のFETであり、MESFETのショットキー接合には逆方向にのみ電圧を加え( $V_{GS} \le 0V$ )、Idを減少させるようにして動作させる。このため図1の等価回路中のそれぞれのダイオードには逆バイアスがかかるためリーク電流しか流れないので以下の特性方程式ではこの電流を無視する。

図1の等価回路を基に、DC特性( $Id-V_{GS}$ 特性及び、 $Id-V_{DS}$ 特性)の実測値へのカーブフィッテイングを行い、動作バイアス点を決定するDCデバイスモデルの作成を行う。

GaAsMESFET等価回路内部に存在するドレイン電流源は $V_{GS}$ や $V_{DS}$ をはじめとしてさまざまな要素によって値が変化する。この変化を記述した式が特性方程式であり、TSpice用DCフィッテイング時において、<math>GaAsMESFETが動作する順バイアス時 ( $V_{dS}>0$ ) では、 $V_{GS} \succeq V_{TH}$ 、 $V_{DS}$ との関係により以下の式で表わされる。

$$\begin{aligned} \mathbf{Id} & \left\{ \begin{array}{l} = \ 0: \ (\ V_{GS} - V_{TH} < O \ ) \\ = \ \mathrm{BETA} \ (\ V_{GS} - V_{TH} \ )^{\ 2} \ (\ 1 - \mathrm{LAMBDA} \cdot V_{\mathrm{DS}} \ ): \\ & \ (O < V_{GS} - V_{TH} < V_{DS} \ ) \\ = \ \mathrm{BETA} \cdot V_{\mathrm{DS}} \ \{ 2 \ (\ V_{GS} - V_{\mathrm{TH}} \ ) \ \} \ (\ 1 - \mathrm{LAMBDA} \cdot V_{\mathrm{DS}} \ ): \\ & \ V_{\mathrm{DS}} \ ): \ (\ O < V_{DS} < V_{GS} - V_{TH} \ ) \end{aligned} \right.$$

なお、 $V_{TH} = VTO - GAMMA \cdot V_{DS}$  ・・・(2.2) (2.1)式、(2.2)式内のパラメータ名を表 1 に示す。

表 1. 特性方程式内のパラメータ名 (DC フィッテイング)

| $V_{GS}$        | ゲート・ソース間電圧                   |

|-----------------|------------------------------|

| $V_{DS}$        | ドレイン・ソース間電圧                  |

| V <sub>TH</sub> | 閾値電圧                         |

| BETA            | トランスコンダクタンス                  |

| LAMBDA          | チャンネル長変調パラメータ                |

| GAMMA           | チャンネル厚変調パラメータ                |

| VTO             | V <sub>DS</sub> =0[V]の時の閾値電圧 |

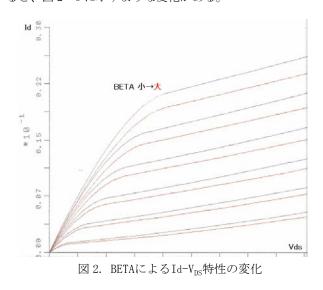

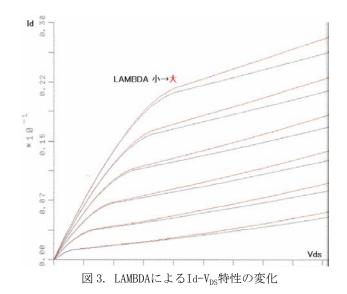

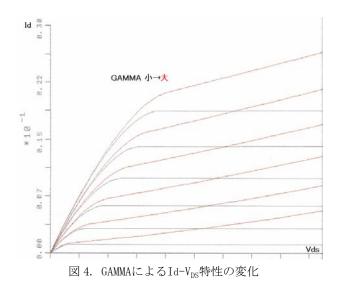

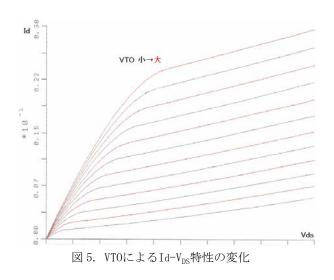

なお、BETA、LAMBDA、GAMMA、VTO は TSpice 用 DC デバイスモデルでは定数として取扱っているが、これら値を変えると、図 2~5 に示すような変化がある。

図 2 より、BETAを大きくすると、 $Id-V_{DS}$ 特性のパラメータである $V_{GS}$ 間の幅及び波形スケールがIdの減少する方向に変化することがわかる。

図3より、LAMBDAを大きくすると、飽和領域での電流の傾きが増加することがわかる。

図 4 より、GAMMAを大きくすると非飽和領域と飽和領域の境界である遷移点が $V_{DS}$ 側に伸び、かつ飽和領域において $V_{DS}$ とともにIdが増加することがわかる。

図5より、VTOを大きくすると飽和領域におけるIdが増加方向に平行移動することがわかる。

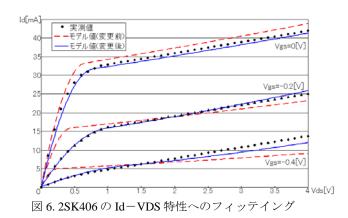

これら 4 つの特性パラメータはTSpiceでは定数として扱っているため、参考文献 2 で指摘されているように、広範囲の $V_{DS}$ 、 $V_{GS}$ に対して実測値との乖離が避けられない。本研究では、簡易モデルであるTSpice用DCデバイスモデルを基とし、かつこれらの 4 つのパラメータを $V_{GS}$ の関数とすることにより広範囲の $V_{DS}$ 、 $V_{GS}$ に対して実測値と良い一致の得られるDCデバイスモデルを作成できることを示す。図 6 にゲート長  $0.3\,\mu$  mのGaAsMESFETである 2SK406 の $Id-V_{DS}$ 特性の実測値にフィッテイングを行った場合のフィッテイングカーブをそれぞれ、4 つのパラメータを定数とした場合(変更前)、 $V_{GS}$ の多項式で表わした場合(変更後)について示す。なお、4 つのパラメータの値については表 2 に示す。

表2 DC カーブフィッテイングに用いたパラメータ

| _ 衣 2. DC ガーノフィッティングに用いたパラケータ |          |                                  |  |  |

|-------------------------------|----------|----------------------------------|--|--|

| パラメータ                         | 変更前 (定数) | 変更後<br>(V <sub>GS</sub> の多項式)    |  |  |

| VTO                           | -0.65    | $1.85 \cdot V_{GS} - 0.76$       |  |  |

| GAMMA                         | 0.02     | $0.5 \cdot V_{GS}^2 + 0.035$     |  |  |

| LAMBDA                        | 0.027    | $-0.375 \cdot V_{GS} + 0.005$    |  |  |

| BETA                          | 0.074    | $(V_{GS}+0.4)^2 \cdot 0.3+0.003$ |  |  |

パラメータを定数とした場合は、図 6に示すように $V_{GS}$  = -0.2V、 $V_{DS}$  = 2V の近傍では実測値との良いフィッテイングが得られるものの、 $V_{GS}$  や $V_{DS}$  がこの点から離れると実測値との乖離が目立つようになる。パラメータを $V_{GS}$  の多項式で表現することにより、図 6 に示される範囲( $-0.4V \le V_{GS} \le 0V$ 、 $0V \le V_{GS} \le 4V$ )全体において実測値に近い、良好なフィッテイングが得られた。しかし、 $V_{GS}$  が -0.4V よ

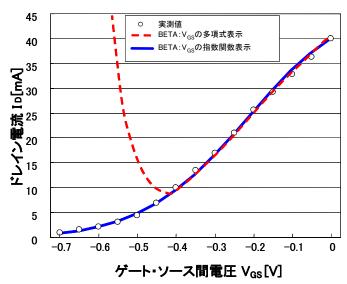

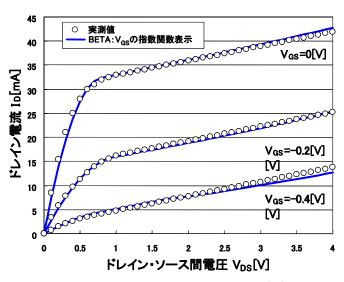

りも小さい領域では、BETAについてIdを $V_{\rm GS}$ の2乗特性で表現する方法では、実測値との乖離が目立つようになる。BETAを $V_{\rm GS}$ の指数関数表示としたときの2SK406のId- $V_{\rm GS}$ 特性へのフィッテイングを図7に、Id- $V_{\rm DS}$ 特性へのフィッテイングを図8に、指数関数表示による改良前後のBETAのパラメータを表3に示す。Idに直接影響を及ぼすBETAについて $V_{\rm GS}$ を変数とした指数関数表示とすることにより、 $V_{\rm GS}$ が一0.4Vよりも小さい領域でも実測値との良好なフィッテイングが得られるようになった。

図 7. 2SK406 のId-V<sub>GS</sub>特性へのフィッテイング

図 8. 2SK406 の $Id-V_{DS}$ 特性へのフィッテイング (BETAを 指数関数表示とした場合)

表 3. BETA のパラメータ表示

| <b> </b>                          |                                                      |  |  |  |  |

|-----------------------------------|------------------------------------------------------|--|--|--|--|

| 改良前のBETA                          | 改良後のBETA                                             |  |  |  |  |

| (V <sub>GS</sub> の多項式表示)          | (V <sub>GS</sub> の指数関数表示)                            |  |  |  |  |

| $(V_{GS}+0.4)^2 \times 0.3+0.003$ | $0.042 \times \exp \{-7.5 (V_{GS} - 0.253) V_{GS}\}$ |  |  |  |  |

このようにGaAsmESFETの特性方程式のパラメータVTO、GAMMA、LAMBDAを $V_{GS}$ の多項式で表わし、さらにBETAを $V_{GS}$ の指数関数で表わすことにより、 $V_{DS}$ 及び $V_{GS}$ の測定領域全域に亘り、精度の高いIdカーブフィッテイングを実現することができた。

#### 2.2 AC カーブフィッテイング

ACカーブフィッテイングでは、図 1 のGaAsMESFET等価 回路中の二つのダイオードをそれぞれ抵抗として扱うが、非常に高抵抗となるため、近似的にはオープンとして取扱うことができる。図 1 におけるGaAsMESFETの等価回路内の容量、 $C_{GS}$ 、 $C_{Gd}$ についてはGaAsMESFETが動作する $V_{GS}$   $\geq$   $V_{TH}$  、 $V_{CD}$   $\geq$   $V_{TH}$  のときは以下の式で表わされる。

$$C_{gs} = \frac{LG \cdot W}{2\sqrt{2}} \left( \frac{q \cdot Nde \cdot \varepsilon}{VBI - VGS} \right)^{\frac{1}{2}}$$

$$C_{gd} = \frac{LG \cdot W}{2\sqrt{2}} \left( \frac{q \cdot Nde \cdot \varepsilon}{VBI - VGD} \right)^{\frac{1}{2}}$$

$$C_{gd} = \frac{EG \cdot W}{2\sqrt{2}} \left( \frac{q \cdot Nde \cdot \varepsilon}{VBI - VGD} \right)^{\frac{1}{2}}$$

$$C_{gd} = \frac{E \cdot (VBI - VGD)}{2q \cdot RP^{2}}$$

$$C_{gd} = \frac{E \cdot (VBI - VGD)}{2q \cdot RP^{2}}$$

$$C_{gd} = \frac{E \cdot (VBI - VGD)}{2q \cdot RP^{2}}$$

(2.3)式、(2.4)、(2.5)式内のパラメータ名と 2SK406 の パラメータ値を表 4 に示す。

表 4 2SK406 の AC カーブフィッテイングのパラメータ

| LG  | ゲート長    | $0.3 \times 10^{-6}$                     |

|-----|---------|------------------------------------------|

| W   | ゲート幅    | $280 \times 10^{-6}$                     |

| q   | 電子の電荷   | $1.6 \times 10^{-19}$                    |

| 8   | 誘電率     | 12. $6 \times 8$ . $854 \times 10^{-14}$ |

| VBI | ビルトイン電圧 | 0.8                                      |

| RP  | 平均射影飛程  | $1.3 \times 10^{-9}$                     |

| Ci  | 内部等価容量  | $1.5 \times 10^{-13}$                    |

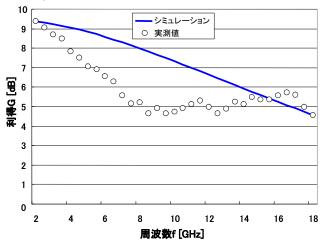

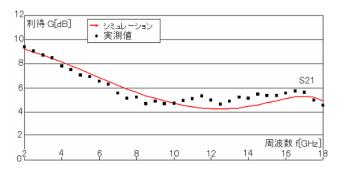

これらの値を用いて周波数応答特性に対するACカーブフィッテイングを行った。図 9 は高周波測定において最も汎用的なSパラメータ( $S_{21}$ )を用い、実測値及び回路シミュレーションにおいて比較的低周波領域(2GHz)でフィッテイングした利得の周波数依存性、つまり周波数応答特性を示す。

図 9. 2SK406 の周波数応答特性

このように実測値とシミュレーションでは  $4\text{GHz} \sim 14\text{GHz}$  の範囲で乖離しているが、高周波測定における測定において、測定プローブ等による浮遊容量や寄生インダクタンスが影響していると考え、シミュレーション回路の出力に $\pi$ 型の C-L-C 回路を付加して実測値と比較した。付加した C-L-C 回路の L を 0.45nH、C を 0.35pF とした場合の周波数応答特性を図 10 に示す。

図 10. C-L-C 回路挿入時の 2SK406 の周波数応答特性

シミュレーションと実測値は良い一致が得られ、これより 実測値においては、測定プローブ等の測定系による特性劣 化が現れていると考えることができる。従って、図 9 に示 すシミュレーションカーブが、測定系の影響のない 2SK406 本来の周波数応答特性であると考えることができる。

#### 2.3 PSpice 上で使用可能なデバイスモデルの作成

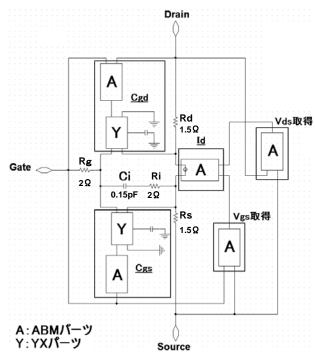

カーブフィッティングした 2SK406 等価回路モデルを PSpice 上で使用可能なデバイスモデルとするため、回路図 設計ツールである OrCAD Capture のモデル編集機能のひと つであるアナログビヘービアモデル (ABM) パーツを用い た。ABM パーツは、パーツ内に関数式を記述し、その計算 結果を出力することができる。引数に Vgs や Vds などの外 部電圧を用い、(2.1) 式の Id に関する関数式をパーツ内 に記述することにより、GaAsMESFET 等価回路中の電圧制御 電流源を表現することができる。また、ABM パーツを用い て、引数として用いる Vgs や Vds の値を回路内から取得す ることができる。Cgs や Cgd などの電圧に依存するリアク タンスを表現するためには、OrCAD Capture のモデル編集 機能として提供されておりリアクタンスの値を任意に変化 させることのできる YX パーツを用いるが、YX パーツその ものには関数式を記述する機能がないので、関数式を記述 できる ABM パーツと組み合わせ、ABM パーツに(2.3)式、 (2.4)式を記述することにより Cgs、Cgd を表現した。

図 11 に PSpice 上で使用可能な 2SK406 デバイスモデルを示す。図 7~図 10 の回路シミュレーション結果は、このデバイスモデルを用いて PSpice 上で回路シミュレーションを実行することにより得られた。このデバイスモデルをサブサーキット化し、PSpice 上のデバイスモデルのライブラリに登録することにより、他の標準登録されたデバイスモデルと同様に PSpice の回路上に呼び出して使用することができるようになった。

図 11. PSpice 上で使用可能な 2SK406 デバイス モデル

# 3. 作成デバイスモデルの増幅回路への適用

実特性にフィッテイングすることにより作成した GaAsMESFET (2SK406) デバイスモデルを最も基本的な増幅 回路であるソース接地増幅回路適用し、性能指標 API[3]を 用いて回路の特性評価を行った。増幅回路の API は(3.1) 式により定義される。

$$API = \frac{G \cdot B}{W} \qquad (3.1)$$

ここで G: 利得 [dB 表示]、B: 3dB 低下帯域、W: 消費電力であり、API は単位消費電力当りの周波数応答特性、言い換えると効率を表す。利得 G を dB 表示としているため、API には以下の特徴がある。

- 1) 利得/損失の基準値が真値表示の1に対して、dB表示では0であるため、利得GをdB表示にすることにより、APIの正/負と利得/損失が対応している。

- 2) 入出力整合が取れた利得 G[dB]、消費電力 W[W]の単位 増幅回路を n 段縦続接続した場合、利得飽和が生じない限り、縦続接続増幅回路の利得は n・W となるため、多段化により帯域劣化が生じないという理想的な場合の縦続接続増幅回路と単位増幅回路の API は一致する。

- 3) W→0 の場合、G を真値表示とすると、 $API \rightarrow \infty$ となってしまうが、G を dB 表示とし、API を増幅回路の利得がある正の領域に限定することで  $W \rightarrow 0$  の時の API の発散を防止することができる。

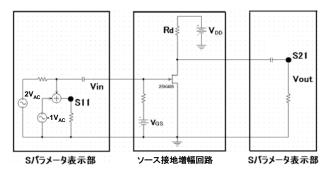

図 12 に PSpice 回路シミュレーションより評価した GaAsMESFET (2SK406) ソース接地増幅回路の構成を示す。

図 12. 評価した GaAsMESFET ソース接地増幅回路の構成

数百MHz以上の広帯域増幅器への適用を念頭として、3dB低下帯域、利得は、入出力を特性インピーダンス  $50\Omega$ で終端したSパラメータ( $S_{21}$ )より求めた。順方向の伝達特性  $S_{21}$  、順方向の反射特性 $S_{11}$ は信号源の電圧をE、出力電圧を $V_{out}$ 、入力電圧を $V_{in}$ とすると、

$$S_{21} = \frac{2v_{out}}{E}, \quad S_{11} = \frac{2v_{in} - E}{E}$$

(2)

と表せる[4]。PSpiceではAC解析より周波数応答特性を求めるが、これは線形解析であるため、入出力比は入力信号の値によらず一定である。これより、E=2と設定することにより $v_{out}$ が $S_{21}$ そのものを表す。また、 $S_{11}=v_{in}-1$ となり、 $v_{in}$ に、-1を加える操作をすることにより、 $S_{11}$ を求めることができる。この操作を表記したものが図 12 中のSパラメータ表示部である。

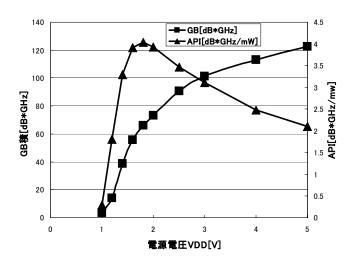

APIに関与するソース接地増幅回路の回路パラメータは、ゲート-ソース間電圧 $V_{GS}$ 、ドレイン電源電圧 $V_{DD}$ 、ドレイン負荷抵抗Rdである。 $V_{DD}$ を主要回路パラメータとし、APIがそのときの $V_{DD}$ に対し最大になるようにRdと $V_{GS}$ を調整しシミュレーションを行った。 $V_{DD}$ に対するAPI最大値を図 13 に示す。参考として増幅器の一般的な性能評価に使用されるGB積についても $V_{DD}$ に対する値を示す。

図13. 評価回路のAPIとGB積

GB積は $V_{DD}$ とともに増加し、やがて飽和するのに対し、APIでは $V_{DD}$ に対して最大となる点が存在する。また、このときの $V_{DD}$ はGB積の飽和点での $V_{DD}$ よりも低いところで得られている。

次にゲート長  $2\mu$ m の MOSFET である 2SK318 を適用した ソース接地増幅回路の API 最大値[3] との比較を表 5 に示す。最も大きな違いは帯域であり、2SK406 を用いた増幅回路が 2SK318 を用いた増幅回路より約 2500 倍大きい。消費電力の観点からは、2SK406 を用いた増幅回路は 2SK318 を用いた増幅回路より 21 倍大きいものの、効率を示す API で評価すると 2SK406 を用いた増幅回路のほうが 124 倍大きくなることがわかった。

表 5. MOSFET (2SK318) 及び GaAsMESFET (2SK406) を用いたソース接地増幅回路の API 最大値の比較

|                 | 2SK318 増幅回路 | 2SK406 増幅回路        |

|-----------------|-------------|--------------------|

| G [dB]          | 2. 88       | 2. 47              |

| B [MHz]         | 5. 43       | $1.42 \times 10^4$ |

| W [mW]          | 0.48        | 10                 |

| API [dB·MHz/mW] | 32. 8       | $4.07 \times 10^3$ |

# 4. まとめ

GaAsMESFETは高速特性に優れたトランジスタであるが、汎用性があり経済的な電子回路シミュレータであるPSpiceで使用可能なGaAsMESFETデバイスモデルは提供されていなかった。大型計算機用電子回路シミュレータであるTSpiceではGaAsMESFETデバイスモデルが存在するが、トランジスタの線形領域において、ゲートーソース間電圧 $V_{CS}$ やドレインーソース間電圧 $V_{DS}$ が広い範囲に亘るとモデル値が実測値と乖離するという課題があった。

今回作成したGaAsMESFETデバイスモデルは、等価回路が簡単なカーティスモデルをベースとするが、トランジスタの特性パラメータであるLAMBDA、GAMMA、VTOを $V_{GS}$ の多項式として表わし、またBETAを $V_{GS}$ を変数とした指数関数として表現することにより、ドレイン電流Idに関して $V_{GS}$ 及び $V_{DS}$ の広い範囲に亘り、実測値との良いカーブフィッテングを得ることができた。このデバイスモデルを回路図設計ツールである0rCAD Captureのモデル編集機能のアナログビへービアモデル(ABM)パーツ、及びYXパーツを用いて表現し、サブサーキット化することにより、PSpiceのデバイスモデルのライブラリに登録することができ、他の標準登録されたデバイスモデルと同様にPSpiceの回路上に呼び出して使用することが可能となった。

今回デバイスモデルを作成したゲート長  $0.3 \mu m$  の GaAsMESFET である 2SK406 とコンベンショナルな MOSFET であるゲート長  $2 \mu m$  の 2SK318 をそれぞれ、最も基本的な増幅回路であるソース接地増幅回路に適用し、帯域、利得、消費電力を一元的に評価することが可能な性能指標 API により特性比較を行った。 GaAsMESFET は高速性に優れ、MOSFET は低消費電力特性に優れていることが確認され、さらに効率という観点からは今回評価した 2SK406 がコンベンショナルな MOSFET を上回ることが確認された。

#### 参考文献

- [1] W.R.Curtice, "A MESFET model for use in the design of GaAs integrated circuits", IEEE Transactions on Microwave Theory and Techniques, MTT-28, p.448-456,1980.

- [2] 藤井恒平、"GaAs FET 用マイクロ波等価回路モデルー その基礎と実際"、サイペック REALIZE 社、2002.

- [3] 大川典男、"小信号電圧増幅回路の帯域利得特性・消費電力に関する性能指標、"電子情報通信学会論文誌 Vol.J92-C No.7 pp.301-303、2009.

- [4] M. Jamal Deen and Tor A. Fieldly, "CMOS RF Modeling, Characterization and Applications", World Scientific Publishing, 2002.